# A reusable verification, emulation and validation flow for ASIC design

**Tomasz Hemperek**

dectris.com

# **Typical setup**

... in my sensor design experience

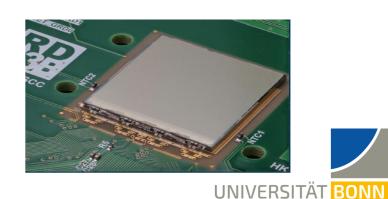

ASIC

PC

ORConf 2023

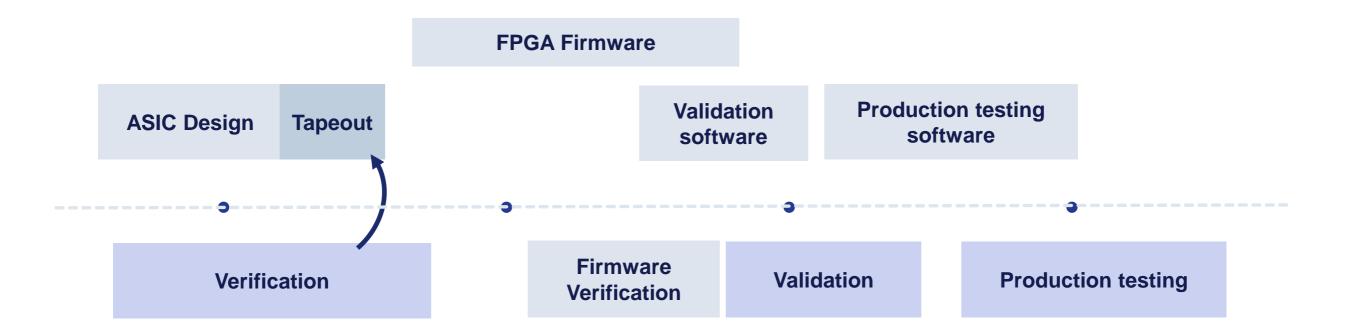

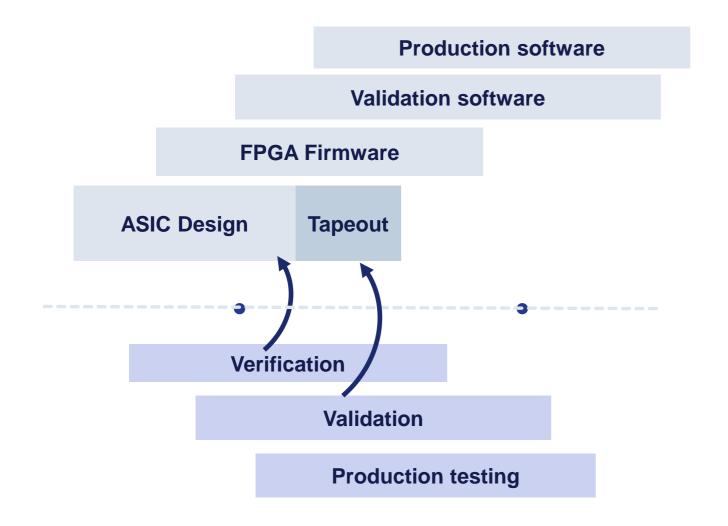

# **Development life cycle**

Multiple teams  $\rightarrow$  communication via specifications  $\rightarrow$  non overlapping codebase

**Different timelines**  $\rightarrow$  very costly late discovered specification issues and bugs

### DECTRIS

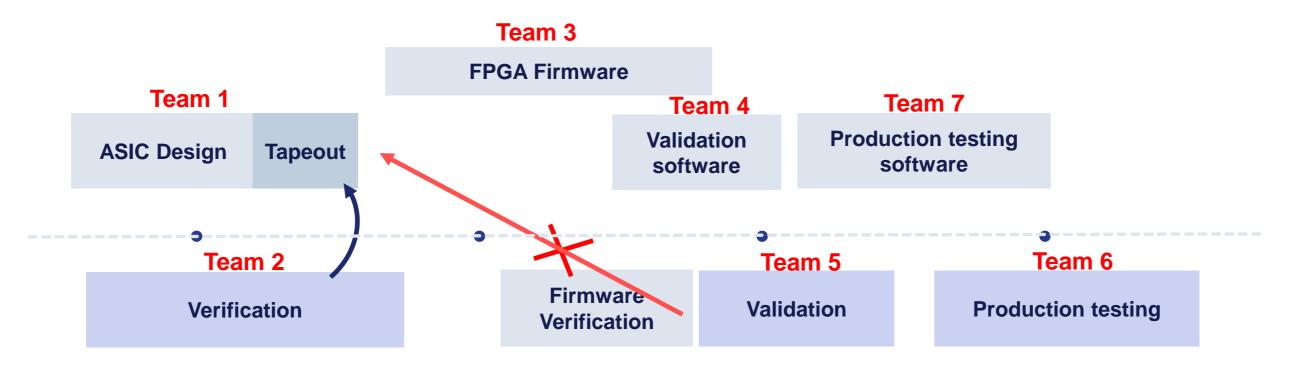

# **Development life cycle**

Multiple teams  $\rightarrow$  communication via specifications  $\rightarrow$  non overlapping codebase

**Different timelines**  $\rightarrow$  very costly late discovered specification issues and bugs

### DECTRIS

# **Development life cycle**

- $\rightarrow$  shorten development time

- $\rightarrow$  improve communication

- $\rightarrow$  early influence on ASIC functionality

- $\rightarrow$  better coverage

Verification is software.

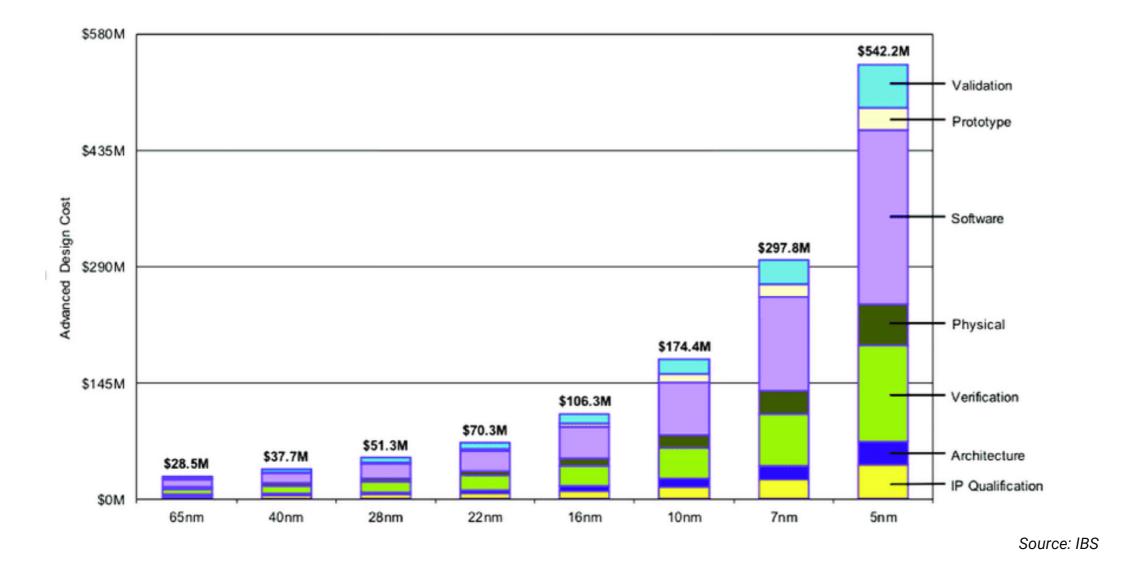

### **Chip Design and Manufacturing Cost**

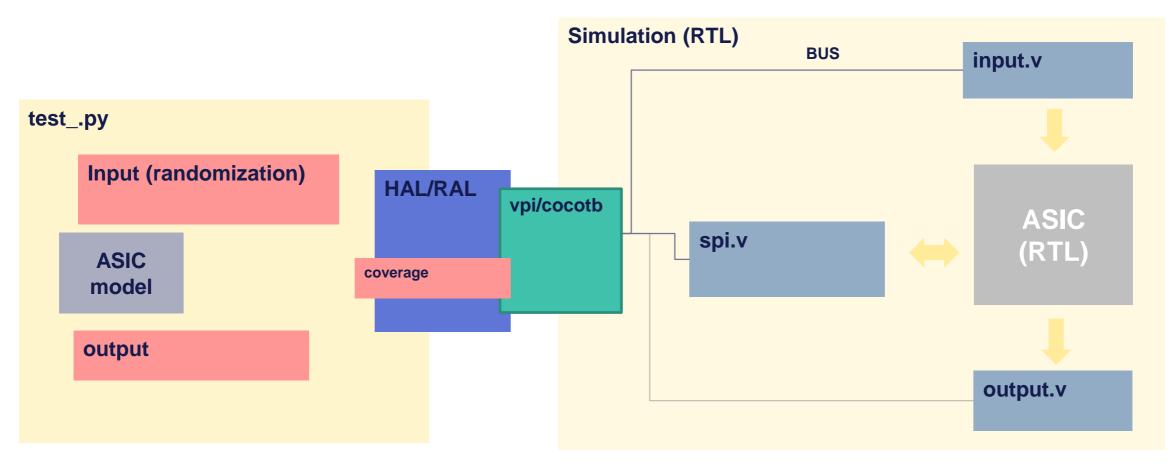

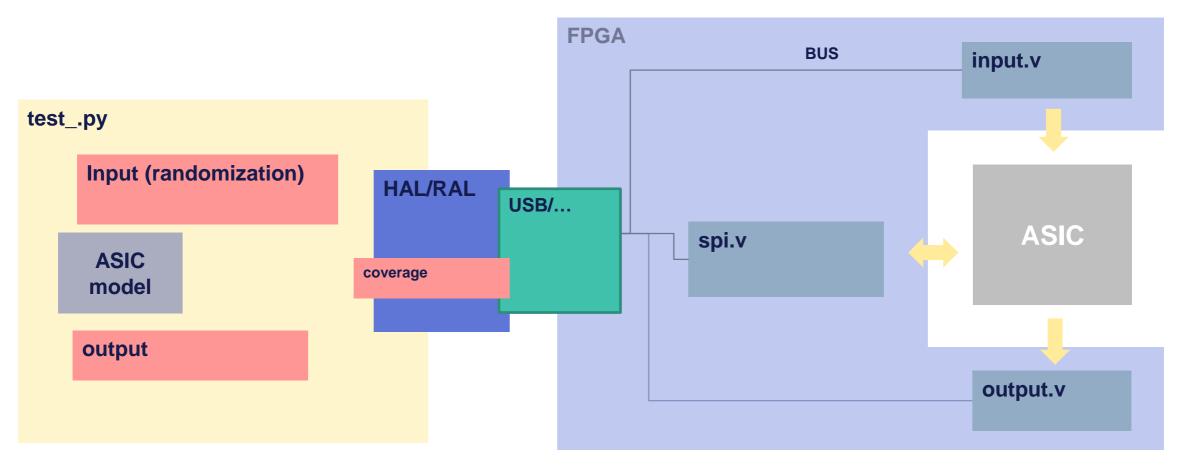

# Simulation/Verification

Move the verification part to the software.

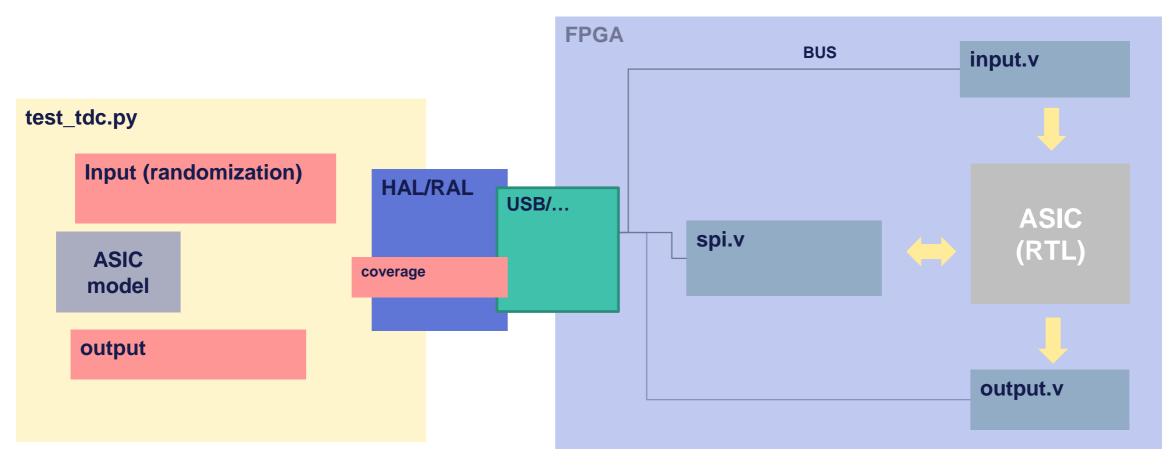

# **Emulation**

# Validation

### **Example use case**

https://github.com/themperek/ORConf23

Disclaimer:

This is a very simple demo.

In large part, this work was done while at the University of Bonn (<u>https://gitlab.cern.ch/silab/tdc\_example/</u>). Some amount of "hackery" is required.

ORConf 2023

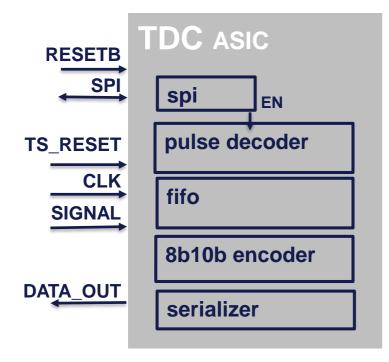

# **TDC / DUT**

- Single channel TDC

- Configured/Enabled by SPI interface

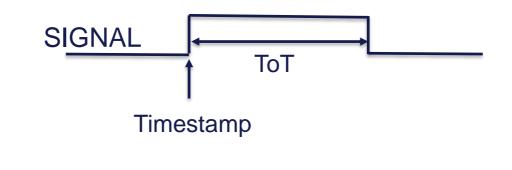

- Input "SIGNAL" sampled with CLK

- Timestamp (16bit) and ToT (8bit) stored to FIFO

- Timestamp reset with "TS\_RESET"

- Data are 8b10b encoded (simple protocol) and serialized

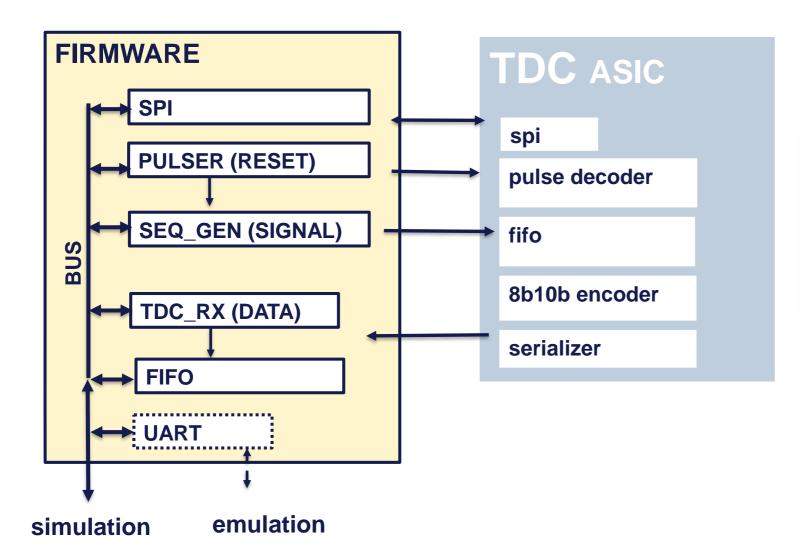

# **Firmware**

Firmware/software modules based on Basil <a href="https://github.com/silab-bonn/basil">https://github.com/silab-bonn/basil</a>

In emulation use UART https://github.com/ultraembedded/core\_dbg\_bridge

# **Example module**

### tdc\_fw\_core.sv:

```

spi sbus #(

.BASEADDR (SPI BASEADDR),

.HIGHADDR (SPI HIGHADDR),

.ABUSWIDTH(32),

.MEM BYTES(16)

spi (

.BUS_CLK(BUS_CLK),

.BUS_RST(BUS_RST),

.BUS ADD(BUS ADD),

.BUS_DATA_IN(BUS_DATA_IN[7:0]),

.BUS DATA OUT(SPI DATA OUT),

.BUS RD(BUS RD),

.BUS_WR(BUS_WR),

.SPI CLK (SPI CLK),

.EXT_START(1'b0),

.SCLK(SCLK),

.SDI (SDI),

.SDO (SDO),

.SEN (),

.SLD (SLD)

);

```

### Hardware Abstraction Layer (HAL)

Every firmware (Verilog) module has a corresponding driver

### basil/HL/spi.py:

....

```

class spi(RegisterHardwareLayer):

```

```

'''Implement serial programming interface (SPI) driver.

```

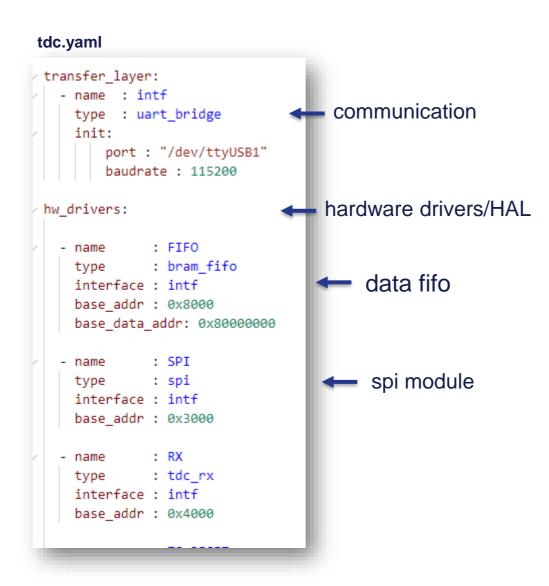

# **Top configuration**

Communication interfaces are separate. Memory address mapping are defined.

# **Register Abstraction (RAL)**

# tdc.yaml registers: - name : CONFIG\_REG type : StdRegister driver : None size : 8 fields: - name : EN size : 1 offset : 0

Can define arbitrary size registers An arbitrary amount of fields Can specify bit order Can specify arrays (repeating fields) Can be initialized (also with configuration file)

### **User experience**

### Initialize:

from basil.dut import Dut

self.chip = Dut("tdc.yaml")

self.chip.init()

Same code for verification and validation.

```

def test readout(self):

self.assertEqual(self.chip["RX"].READY, 1)

self.chip["CONFIG REG"]["EN"] = 1

Set configuration and send via SPI

self.write_config()

Check 8b10b sync

self.assertEqual(self.chip["RX"].READY, 1)

Enable data receiving

self.chip["RX"].ENABLE RX = 1

self.chip["TS_RESET"].DELAY = 1

Timestamp reset

self.chip["TS RESET"].WIDTH = 1

self.chip["SIGNAL_SEQ"].set_data([0x00,0x07,0x00,0

self.chip["SIGNAL SEQ"].REPEAT = 1

Configure SIGNAL pattern

self.chip["SIGNAL_SEQ"].SIZE = 8 * 8 + 8 * 16

self.chip["SIGNAL_SEQ"].EN_EXT_START = 1

self.chip["FIF0"].RESET

self.chip["TS_RESET"].START

while not self.chip["SIGNAL_SEQ"].READY:

Wait for sequence to finish

pass

Check FIFO fill level

self.assertEqual(self.chip["FIF0"].FIF0_SIZE, 16)

Get data from FIFO

data = self.chip["FIF0"].get data()

```

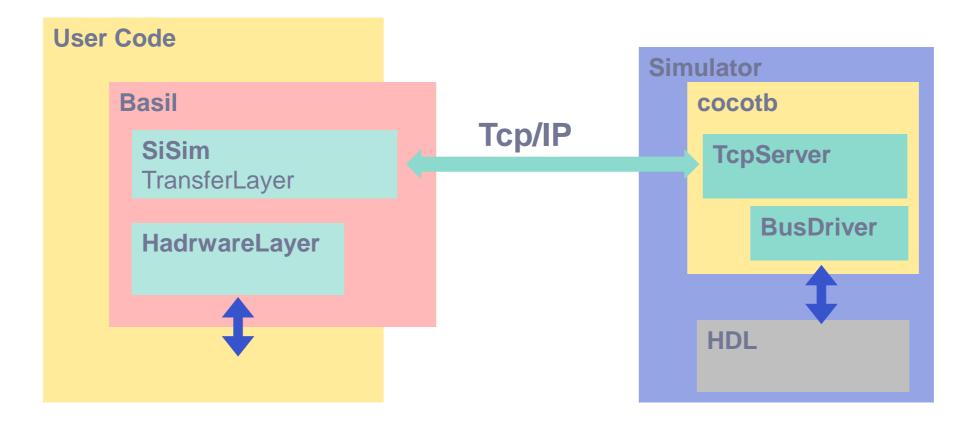

### How simulation works

UART interface is replaced with the simulation interface.

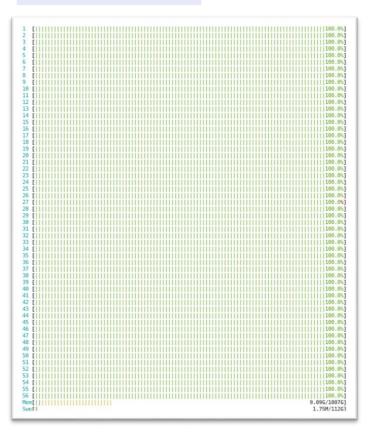

# **Continuous integration**

https://github.com/themperek/ORConf23/actions

| Triggered via push 9 minutes ago     | 526 master | Status<br>Success | Total duration<br>8m 46s | Artifacts<br><b>4</b> |                  |

|--------------------------------------|------------|-------------------|--------------------------|-----------------------|------------------|

| ci.yml build firm                    | iware (    | (F4PGA)           | tes                      | t on FPC              | GA (self-hosted) |

| <ul> <li>build-fw</li> </ul>         | 6m 21s     | • 🛛 emulation     | 2m 1(                    | )s                    |                  |

| simulation                           | 3m 34s     |                   |                          |                       |                  |

| Artifacts<br>Produced during runtime |            |                   |                          |                       |                  |

| Name                                 |            |                   |                          | Size                  |                  |

| 💮 bitfile                            |            |                   |                          | 2.09 MB               |                  |

| build-reports                        |            |                   |                          | 8.1 MB                | reports          |

| emulation-reports                    |            |                   |                          | 35.9 KB               |                  |

| simulation-reports                   |            |                   |                          | 1.59 KB               |                  |

### **Test reports**

### tomasz.hemperek> pytest -v test

| <pre>test/test_tdc.py::TestTDC::test_parameterized_0 PASSED</pre> | [ 16%] |

|-------------------------------------------------------------------|--------|

| <pre>test/test_tdc.py::TestTDC::test_parameterized_1 PASSED</pre> | [ 33%] |

| <pre>test/test_tdc.py::TestTDC::test_parameterized_2 PASSED</pre> | [ 50%] |

| <pre>test/test_tdc.py::TestTDC::test_parameterized_3 PASSED</pre> | [ 66%] |

| <pre>test/test_tdc.py::TestTDC::test_simple_readout PASSED</pre>  | [ 83%] |

| <pre>test/test_tdc.py::TestTDC::test_spi PASSED</pre>             | [100%] |

------ 6 passed in 10.00s -----

### report.html

### Report generated on 12-Sep-2023 at 14:11:19 by pytest-html v4.0.1

### Environment

| Python   | 3.8.15                                                                                                     |

|----------|------------------------------------------------------------------------------------------------------------|

| Platform | Linux-4.18.0-477.13.1.el8_8.x86_64-x86_64-with-glibc2.17                                                   |

| Packages | <ul><li> pytest: 7.4.0</li><li> pluggy: 1.3.0</li></ul>                                                    |

| Plugins  | <ul> <li>cocotb-test: 0.2.3</li> <li>metadata: 3.0.0</li> <li>html: 4.0.1</li> <li>xdist: 3.3.1</li> </ul> |

### Summary

### 6 tests took 00:00:09.

(Un)check the boxes to filter the results.

| 🔽 0 Failed, 🔽 6 Passed, 🔽 0 Skipped, 🔽 0 Expected failures, 💟 0 Unexpected passes, 💟 0 Errors, 💟 0 Reruns 👘 Show all details 🖉 Hide all detail |                                                          |          |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|-------|--|

| Result 🔺                                                                                                                                       | Test                                                     | Duration | Links |  |

| Passed                                                                                                                                         | test/test_tdc.py::TestTDC::test_parameterized_0          | 00:00:02 |       |  |

| Passed                                                                                                                                         | test/test_tdc.py::TestTDC::test_parameterized_1          | 00:00:02 |       |  |

| Passed                                                                                                                                         | test/test_tdc.py::TestTDC::test_parameterized_2          | 00:00:02 |       |  |

| Passed                                                                                                                                         | test/test_tdc.py::TestTDC::test_parameterized_3 00:00:02 |          |       |  |

| Passed                                                                                                                                         | test/test_tdc.py::TestTDC::test_simple_readout           | 00:00:02 |       |  |

| Passed                                                                                                                                         | test/test_tdc.py::TestTDC::test_spi                      | 00:00:01 |       |  |

# **Coverage and Randomization**

### Define covergroup:

@vsc.covergroup class cov(object): def \_\_init\_\_(self): self.with\_sample(dict(data=vsc.bit\_t(8))) self.data\_cp = vsc.coverpoint(self.data, bins=dict(data=vsc.bin\_array([8], [0, 255])))

### Sample:

```

@parameterized.expand([[x] for x in range(4)])

def test_parameterized(self, data):

self.assertEqual(self.chip["RX"].READY, 1)

```

self.cover.sample(data \* 32)

ret = self.rw\_dut\_spi(0x91)

self.assertEqual(ret, 0x91)

| PyUCIS Viewer _               |          |             |  |  |  |  |  |

|-------------------------------|----------|-------------|--|--|--|--|--|

| <u>F</u> ile                  |          |             |  |  |  |  |  |

| Name                          | Coverage | Status      |  |  |  |  |  |

| <ul> <li>TYPE: cov</li> </ul> | 50.00%   | 50%         |  |  |  |  |  |

| ▼ CVP: data_cp                | 50.00%   | <b>5</b> 0% |  |  |  |  |  |

| а                             | 0        | 0           |  |  |  |  |  |

| b                             | 2        | 2           |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

|                               |          |             |  |  |  |  |  |

PyVSC: <a href="https://github.com/fvutils/pyvsc">https://github.com/fvutils/pyvsc</a>

# **Testing with pytest**

### **Tests parametrization:**

@parameterized.expand([[x] for x in range(4)])

def test\_parameterized(self, data):

self.assertEqual(self.chip["RX"].READY, 1)

### **Parallel execution :**

pip install pytest-xdist

pytest -n auto

### Conclusions

- Moving teams together for better collaboration

- Verification is software, let firmware/software contribute early

- Reused for validation and production testing

- Understand limitations

- Can be an organizational challenge

- Can be done with all open tools and modern infrastructure

- Successfully used to develop and test ASICs (example: https://doi.org/10.1016/j.nima.2020.164721)

Contact: Mail: <u>tomasz.hemperek@dectris.com</u> LinkedIn: <u>https://linkedin.com/in/hemperek</u>

# Thank you for your attention!