## OpenRISC Update

What Happened?

Stafford Horne

## What is ORConf?

# Since 2012

ORConf ➤ OpenRISC Project Conference

## What is OpenRISC?

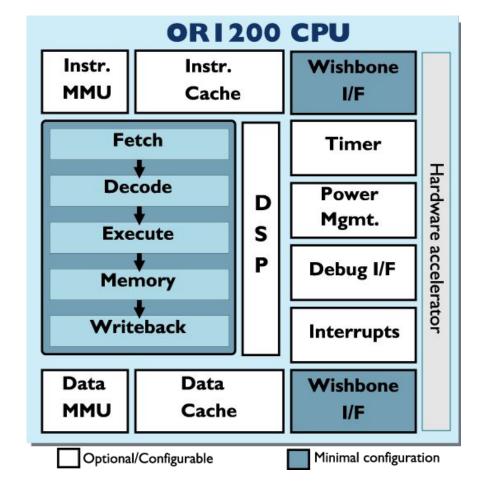

Officially OpenRISC 1000 is an open source RISC architecture:

- 32-bit <del>/ 64-bit</del>

- 32 General Purpose Registers

- Delay Slot

- Instruction & Data MMU

- Linux support since 2010

- o 50mhz, 5 secs

- Open Implementations: mor1kx, or1200, marocchino

Read More: https://raw.githubusercontent.com/openrisc/doc/master/openrisc-arch-1.1-rev0.pdf

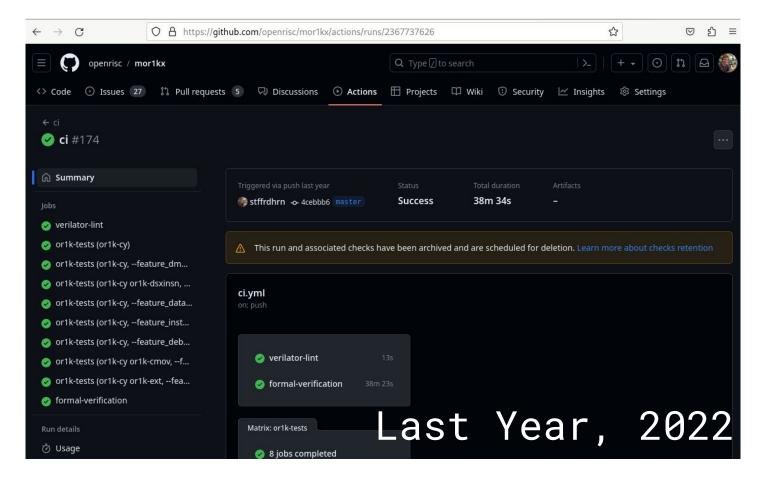

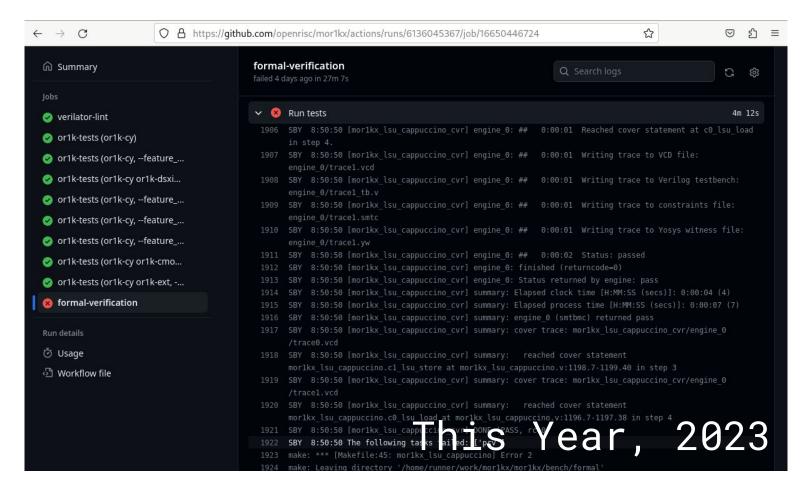

#### Mor1kx - Formal Verification

#### Mor1kx - Formal Verification

## GLIBC OpenRISC Port

### GLIBC OpenRISC Port

```

inutils-gdb - [mosh] root@b34def5835e8: /tmp - shorne@antec:~ - mosh-client -# 10.0.0.27 | 10.0.0.27 60001 - 97×28

300 10.0.0.5

# summary

1 FAIL

4148 PASS

31 UNSUPPORTED

16 XFAIL

2 XPASS

< shorne@antec ~/work/gnu-toolchain > cat log/test--20211226-162029.log

2021-12-26T16:20:29+09:00

# test start:

# failures

FAIL: posix/tst-execveat

# test finish: 2021-12-29T12:54:08+09:00

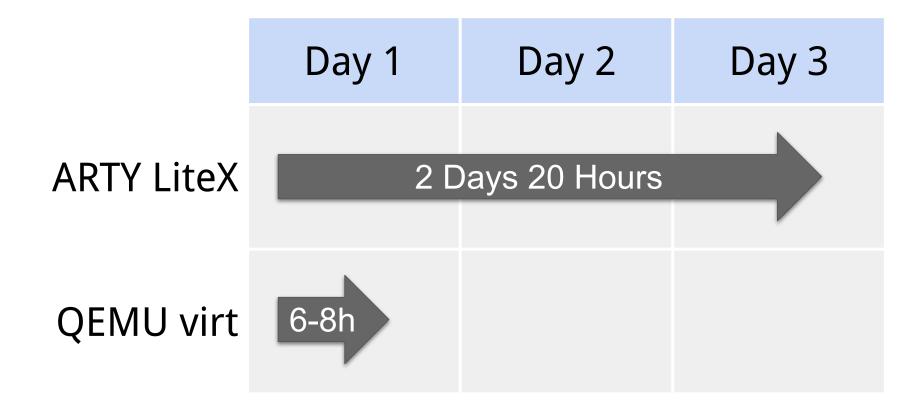

# test duration: 2 days 20 hours 33 minutes and 39 seconds

# test for file: tests.sum

# test wrapper: /home/shorne/work/anu-toolchain/alibc/scripts/cross-test-ssh.sh --timeoutfactor

300 10.0.0.5

# summary

1 FAIL

4148 PASS

31 UNSUPPORTED

16 XFAIL

2 XPASS

< shorne@antec ~/work/gnu-toolchain >

$ mutt 1$ irssi 2!$ shorne@antec:~/work/ 3*!$ shorne@antec:~/work/gnu-toolchain 4-!$ shorn

```

#### What's New - QEMU virt and PCI

```

Starting sntp: sntp 4.2.8p15@1.3728-o Tue Feb 28 21:48:05 UTC 2023 (1)

1970-01-01 00:00:02.507473 (+0000) +847106404.451040 +/- 564737602.984043 pool.ntp.org 82.219.4.30 s2 no-leap

mounting home work nfs ...

enabling login for shorne ...

setting up sshkeys ...

setting coredumps ...

Starting sshd: OK

Welcome to Linux on OpenRISC

buildroot login: shorne

__/|__^__/__/__/__/__/__/

/ /_/ / __/ / '_/__/ \/ // // , _/ / /

__/_/ /_/_\_\ |___/_/_/\أ_| /_/

32-bit OpenRISC CPUs on a QEMU Virt Platform

Linux buildroot 6.5.0-11938-q65d6e954e378 #63 SMP Wed Sep 6 08:11:52 BST 2023 openrisc GNU/Linux

$ cat /proc/interrupts

CPU0

CPU1

CPU2

CPU3

1280

1878

1695 or1k-PIC-level 1 ompic_ipi

1708

2:

25

72 or1k-PIC-level 2 ttvS0

0

0 or1k-PIC-level 3 96005000.rtc

110

66 or1k-PIC-level 11 virtio0

14:

16 or1k-PIC-level 14 virtio1

$ lspci -k

00:00.0 Class 0600: 1b36:0008

00:01.0 Class 0200: 1af4:1000 virtio-pci

0!$ mutt 1$ irssi 2*!$ shorne@antec:~/work/linux 3-!$ shorne@antec:~/work/ 4!$ shorne@antec:~/work/ Fri 09/08/23 | 11:40:47

```

#### **GLIBC Test Run Times**

#### What's New

- Formal verification of mor1kx using yosys

- GLibc port upstreamed

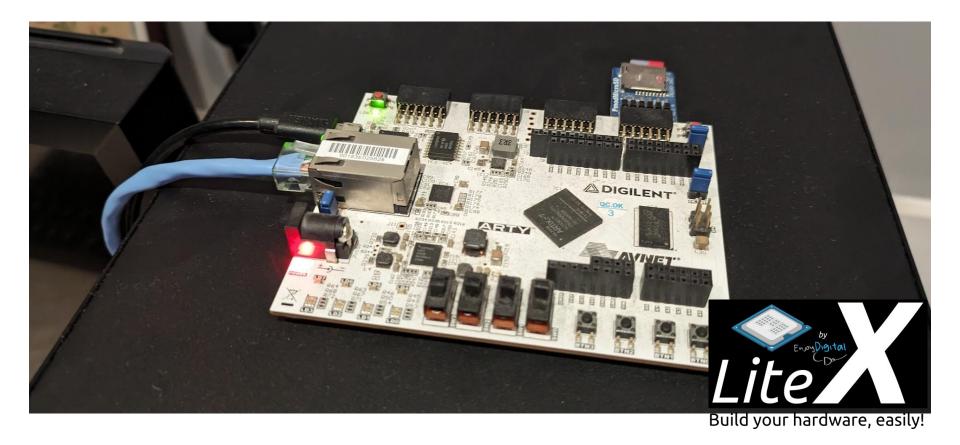

- QEMU virt platform 4 cores

- PCI support added

- Mailing List moved from librecores.org to linux-openrisc@vger.kernel.org

- Or1ksim fixups and container images

- OpenRISC specification update 1.4

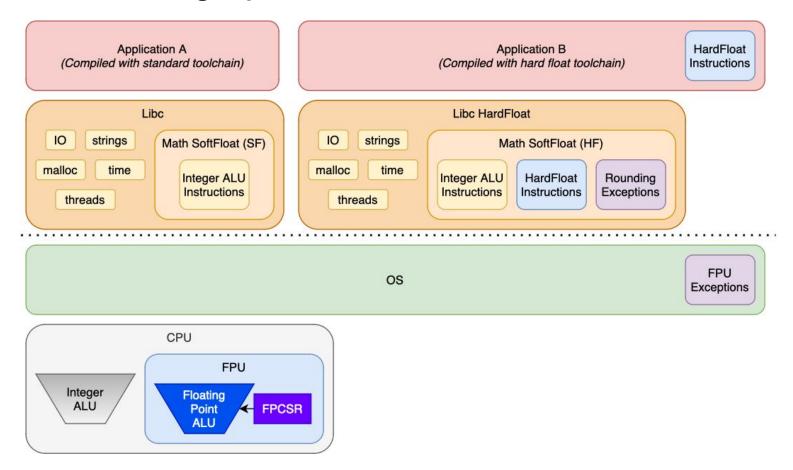

## What's coming up - FPU Port

## What's coming up!

- Glibc FPU Support Upstreaming

- Improve Formal Verification

- o OpenRISC Formal

- Continued Improvements

#### Stafford Horne

- Open source developer since University

- OpenRISC since 2015

- Maintainer of OpenRISC ports for everything!

- Two Kids

## Interested in OpenRISC?

@stffrdhrn

https://openrisc.io

https://stffrdhrn.github.io

@shorne@mastodon.social

openrisc@lists.librecores.org